Contents

hide

The 62256A is a CMOS static RAM organized 32K-word × 8-bit. It realizes higher performance and low power consumption by employing 0.8 µm Hi-CMOS process technology. The device, packaged in an 8 × 14 mm TSOP with a thickness of 1.2 mm, 450-mil SOP (footprint pitch width), 600-mil plastic DIP, or 300-mil plastic DIP, is available for high-density mounting. TSOP package is suitable for cards, and reverse type TSOP is also provided. It offers low power standby power dissipation; therefore, it is suitable for battery backup systems.

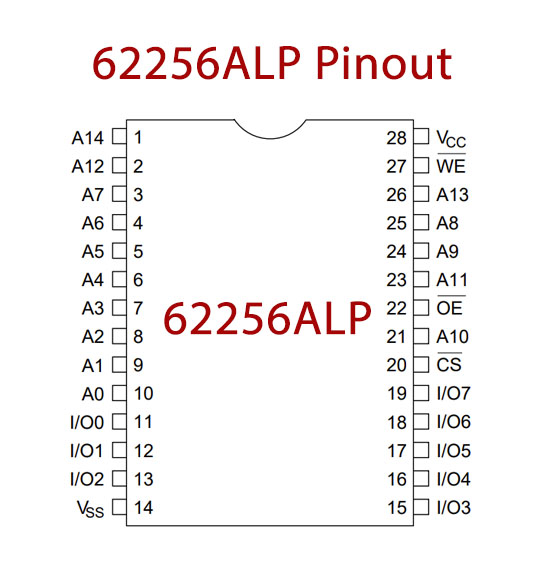

62256 Pinout

62256 Pin Configuration

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | A14 | Address Pin 14 |

| 2 | A12 | Address Pin 12 |

| 3 | A7 | Address Pin 7 |

| 4 | A6 | Address Pin 6 |

| 5 | A5 | Address Pin 5 |

| 6 | A4 | Address Pin 4 |

| 7 | A3 | Address Pin 3 |

| 8 | A2 | Address Pin 2 |

| 9 | A1 | Address Pin 1 |

| 10 | A0 | Address Pin 0 |

| 11 | I/O 0 | Data Inputs/Outputs 0 |

| 12 | I/O 1 | Data Inputs/Outputs 1 |

| 13 | I/O 2 | Data Inputs/Outputs 2 |

| 14 | VSS | Ground Pin |

| 15 | I/O 3 | Data Inputs/Outputs 3 |

| 16 | I/O 4 | Data Inputs/Outputs 4 |

| 17 | I/O 5 | Data Inputs/Outputs 5 |

| 18 | I/O 6 | Data Inputs/Outputs 6 |

| 19 | I/O 7 | Data Inputs/Outputs 7 |

| 20 | CS’ | Chip Select Pin |

| 21 | A10 | Address Pin 10 |

| 22 | OE’ | Output Enable Pin |

| 23 | A11 | Address Pin 11 |

| 24 | A9 | Address Pin 9 |

| 25 | A8 | Address Pin 8 |

| 26 | A13 | Address Pin 13 |

| 27 | WE’ | Write Enable Pin |

| 28 | VCC | Power Supply Pin |

62256 Key Feature

- High speed: Fast Access time 85/100/120/150 ns (max)

- Low Power

- Standby: 5 µW (typ) (L/L-SL version)

- Operation: 40 mW (typ) (f = 1 MHz)

- Single 5 V supply

- Completely static memory

- No clock or timing strobe required

- Equal access and cycle times

- Common data input and output: Three state output

- Directly TTL compatible: All inputs and outputs

- Capability of battery back up operation

You can download this datasheet for 62256 32Kx8 100ns Low-Power CMOS RAM – Datasheet from the link given below: